**Scientific Control Corporation**

Per uip. Ripohon

Digital Computer SCC 650

DERMINAL RADIO INT : S WEST 61st STREET NEW YORK, N. Y. 10023

## INTRODUCTION

The SCC 650 is a powerful twelve bit binary computer which offers many features found only in more expensive equipment: a high speed magnetic core memory with a cycle time of 1.75 microseconds, a versatile and complete instruction repertoire to simplify programming, an input/output interface which permits the use of an unlimited variety of peripheral equipment, and an understandable design for ease in use and maintenance.

In the SCC 650, special emphasis has been placed upon providing a computer system which can adapt to changing needs in the field.

A comprehensive software package is provided with each hardware system. It is designed to take full advantage of the hardware capabilities of the SCC 650 while providing the user with a convenient means of communication with the hardware system.

# **FEATURES**

## Large Memory Capacity

The basic memory module of the SCC 650 contains 4,096 twelve-bit words. The memory capability is expandable to 32,768 words in 4,096 word increments. In keeping with the corporate modular design philosophy, memory expansion may be made in the field.

#### All Silicon Semiconductors

All circuits utilize reliable, silicon semiconductors mounted on printed circuit plug-in cards. The system is highly maintainable at any modular level.

#### **Fully Parallel Operation**

All arithmetic and logical operations, together with high speed data transfers between memory and the various registers, are completed in parallel.

#### Hardware Index Register

In addition to providing address modification for memory reference instructions, the index register is a valuable aid in logical operation. A special set of instructions provide logical and arithmetic operations which use the index register and the accumulator as operands.

## **Priority Interrupt Channels**

The interrupt channel, included as standard equipment, may be activated externally by an external device or internally by a memory protect error.

A priority facility is incorporated to permit external devices to command the computer to transfer to a specific subroutine. Using this facility priority channels can be added which are fully nested. That is, a higher priority channel may interrupt lower priority interrupt routines and the lower priority routine will be resumed after completion of the higher priority function.

### **Memory Protect Feature**

Hardware memory protection is provided for lower numbered memory positions. The protect feature allows the reading of instructions or data from the protected area but inhibits any writing into the protected area of memory. Attempting to write into the protected area causes a program interrupt, allowing the programmer to take corrective action as required. The memory protect feature may be enabled or disabled from a switch on the control console.

## **Direct Memory Access Feature**

The direct memory access feature permits high speed data transfer between memory and external devices. This access channel operates on a cycle stealing basis. As a result, the external device is not required to wait until the present instruction is complete before control of the memory is transferred to the external device. Complete isolation between memory banks allows the computer to continue undisturbed if the external device requests a memory bank other than the one being used by the processor. Also, memory overlap can occur when two or more external devices request different memory modules simultaneously. Therefore, each of eight different devices can transfer data simultaneously at a rate of 570,000 twelve-bit words per second for a total rate of 4.560,000 words/second.

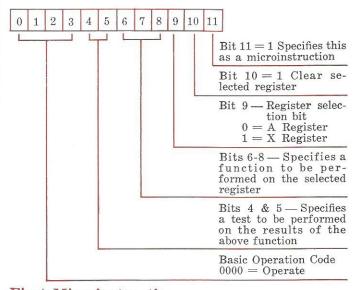

## Micro-Programmable Instructions

All instructions which do not reference memory may be micro-programmed. This group of instructions allows the computer to execute up to four non-memory instructions in a single computer cycle. It also provides the programmer with a variety of bit-manipulation, shift, skip, test, and I/0 instructions.

# Flexible Subroutine Linkages

A single instruction executes a transfer to a subroutine in any core bank and provides the mechanism for a single instruction return to the calling program.

## Four Addressing Modes

The addressing techniques employed in the SCC 650 computer permit several modes of addressing — indirect, direct, relative, indexed, or indirect indexed.

#### **Functional Control Console**

The control console is designed as a functional manmachine interface. The addressable registers are continuously displayed on the control console. These register displays are arranged for quick operator recognition of their contents. Special switches are provided for a fast, convenient means of entering information into memory or examining the contents of memory.

The computer may be operated either in run or singlestep modes.

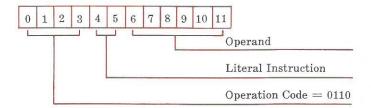

#### Literal Instructions

Several literal instructions are incorporated which use the last six bits of the instruction as the operand. This feature allows high speed, one character arithmetic or logical operations.

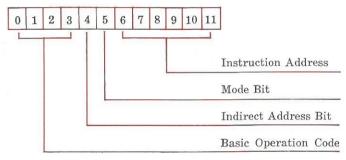

## BASIC INSTRUCTION FORMAT

The basic instruction format is as follows:

In addition to the mode specification bit in the basic instruction, an index state or an indirect index state may be initiated through the status register. When the index state is in effect, the index register is used in lieu of the P counter for address modification.

# ADDRESSING MODES

## **Primary Address**

Each of the four possible addressing modes is based on the concept of a "primary address." The primary address of an instruction is defined to be any address which can be formed using the instruction address and the available address modification registers.

#### **Direct Mode ...** Mode Bit = 0

Primary address is determined by the instruction address. In the direct mode, the primary address always refers to the first 64 locations of memory bank zero.

#### **Index Mode**

Primary address is the sum of the instruction address and the contents of the index register. It will always be in the same memory bank as the instruction.

#### Relative Mode

Primary address is the sum of the instruction address and the address from which the instruction was taken. It will always be in the same memory bank as the instruction. If the primary address is the instruction address plus one, the location counter skips the next word in the instruction sequence. In this way both operands and full addresses may be included "in-line."

#### **Indirect Mode**

The indirect address bit is always applied after the contents of the primary address has been obtained. If the indirect address bit is zero, the contents of the primary address is used as the operand of the instruction. If the indirect address bit is a one, the contents of the primary address is interpreted not as an operand but as the 12 low-order bits of an operand address. The 3 high-order bits of the operand address are specified by the indirect bank register.

#### **Indirect Indexed Mode**

In this mode, after the contents of the primary address are obtained, the contents of the index register are added to form the operand address. As in indirect mode, the 3 high-order bits of the operand address are specified by the indirect bank register.

# INSTRUCTIONS

The instruction repertoire of the SCC 650 is described below. The conventions used in instruction description are as follows:

- (1) A register name enclosed in parentheses denotes the contents of the register.

- (2) Subscription is used to denote bit positions within a register.

- (3) The right arrow symbol, "→", is read "is transferred into."

- (4) The letter "Q" denotes the effective address, i.e., Q denotes the memory address used in the execution of the instruction.

#### **Arithmetic Instructions**

| Instruction                                                                                                                                       | Mnemonic | Cycles | Op Code |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|---------|

| $\frac{\text{Add to Accumulator}}{\text{(A) + (Q)} \rightarrow \text{A}}$ $\text{(Q) } \rightarrow \text{Q}$                                      | ADD      | 2      | 1001    |

| $\frac{\text{Subtract from}}{\text{Accumulator}} \\ \frac{(A) - (Q)}{(Q) \rightarrow A}$                                                          | SUB      | 2      | 1101    |

| $\frac{\text{Exclusive OR with}}{\text{Accumulator}}$ $\frac{\text{(A)} \oplus \text{(Q)} \rightarrow \text{A}}{\text{(Q)} \rightarrow \text{Q}}$ | XOR      | 2      | 1011    |

| AND with Accumulator                                                                                                          | AND     | 2 | 1111 |

|-------------------------------------------------------------------------------------------------------------------------------|---------|---|------|

| $egin{array}{ll} (\mathrm{A})  ullet (\mathrm{Q}) &  ightarrow \mathrm{A} \ (\mathrm{Q}) &  ightarrow \mathrm{Q} \end{array}$ |         |   |      |

| Memory Increment<br>and Skip on Zero                                                                                          | MIN     | 3 | 1000 |

| $\overline{(Q)} + 1 \rightarrow Q$                                                                                            |         |   |      |

| $(A) \to A$ If (Q) = 0, (P)                                                                                                   | + 2 → P |   |      |

| If $(Q) \neq 0$ , $(P)$                                                                                                       |         |   |      |

## Load and Store Instructions

| Luau and Store II                                        | isti uctions | 5                     |          |

|----------------------------------------------------------|--------------|-----------------------|----------|

| Instruction                                              | Mnemonic     | Cycles                | Op Code  |

| $\frac{\text{Load Accumulator}}{(Q) \to A}$ $(Q) \to Q$  | LDA          | 2                     | 1100     |

| $\frac{\text{Store Accumulator}}{(A) \to Q}$ $(A) \to A$ | STA          | 2                     | 0111     |

| $\frac{\text{Load Index}}{(Q) \to X}$ $(Q) \to Q$        | LDX          | 2                     | 0010     |

|                                                          | STX          | 2                     | 0011     |

| Instruction                                              | Mnemonic     | Cycles                | Op Codes |

| $\frac{\text{Jump Forward}}{Q \to P}$ $(A) \to A$        | JMF          | 1                     | 0100     |

| Note: If Bit $4 = 0$                                     | Q = (P)      | + (INS                | 6-11     |

| $\frac{\text{Jump Backward}}{Q \to P}$ (A) $\to$ A       | JMB          | 1                     | 0101     |

| Note: If Bit $4 = 0$ ,                                   | Q = (P) -    | (INS) <sub>6-11</sub> |          |

| Jump and Store                                     | JSL |  |

|----------------------------------------------------|-----|--|

| Location                                           |     |  |

| $\overline{\text{(P)}} + 1 \rightarrow \text{(Q)}$ |     |  |

| $Status \rightarrow Q + 1$                         |     |  |

| $Q + 2 \rightarrow P$                              |     |  |

| $(A) \rightarrow A$                                |     |  |

| Return Jump                  | JRT | 3 | 1110 |

|------------------------------|-----|---|------|

| $(Q) \rightarrow P$          |     |   |      |

| $(Q + 1) \rightarrow Status$ |     |   |      |

| $(A) \rightarrow A$          |     |   |      |

3

1010

#### Literal Instruction Format

| $R_4$ | $R_5$ | Instruction          | Mnemonic |

|-------|-------|----------------------|----------|

| 0     | 0     | AND Literal          | ANL      |

| 0     | 1     | EXCLUSIVE OR Literal | XOL      |

| 1     | 0     | LOAD A Literal       | LDL      |

| 1     | 1     | ADD Literal          | ADL      |

| Instruction $\frac{AND \text{ Literal}}{(INS)_{6-11}} \cdot (A) \to A$                            | Mnemonic<br>ANL | Cycles 1 | R <sub>4</sub> R <sub>5</sub> 0 0 |

|---------------------------------------------------------------------------------------------------|-----------------|----------|-----------------------------------|

| $\frac{\text{Exclusive OR, Literal}}{(\text{INS})_{^{6-11}} \oplus (\text{A}) \to \text{A}}$      | XOL             | 1        | 0 1                               |

| $\frac{\text{Load A, Literal}}{(\text{INS})_{6-11} \to \mathbf{A}}$                               | LDL             | 1        | 1 0                               |

| $\frac{\text{Add, Literal}}{(\text{INS})_{\text{\tiny 6-II}}} + \text{ (A)} \rightarrow \text{A}$ | ADL             | 1        | 1 1                               |

## First Microinstruction

Select the register defined by Bit 9

0 = A Register

1 = X Register

#### **Second Microinstruction**

Perform one of eight functions as specified by Bits 6-8.

| 000 | Test Selected Register only.                                                   |

|-----|--------------------------------------------------------------------------------|

| 001 | Increment Selected Register (Sel Reg) $+ 1 \rightarrow \text{Sel Reg}$         |

| 010 | Add Unselected Register to Selected Register (A) $+$ (X) $\rightarrow$ Sel Reg |

| 011 | Exclusive OR A & X (A) $\oplus$ (X) $\rightarrow$ Sel Reg                      |

| 100 | One's complement of Selected<br>Register (Sel Reg) $\rightarrow$ Sel Reg                                                                      |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 101 | Two's complement of Selected Register (Sel Reg) $+ 1 \rightarrow$ Sel Reg                                                                     |

| 110 | Complement Selected Register and Exclusive OR with Unselected Register $\overline{(A) \oplus (X)}  \to \operatorname{Sel} \operatorname{Reg}$ |

| 111 | Subtract Selected Register from<br>Unselected Register<br>(Unsel Reg) – (Sel Reg) → Sel Reg                                                   |

## Third Microinstruction

Test the results of the above functions and skip as follows:

| $R_4$ | $\mathbb{R}_5$ |                         |

|-------|----------------|-------------------------|

| 0     | 0              | No Skip                 |

| 0     | 1              | Skip if positive $(>0)$ |

| 1     | 0              | Skip if negative        |

| 1     | 1              | Skip if Zero            |

## Fourth Microinstruction

Clear selected register if specified by Bit 10. If bit 10 = 0, do not clear selected register.

# Commonly Used Microinstructions — One Cycle

| Instruction<br>Code | Description                                  | Instruction<br>Code | Description                                                |

|---------------------|----------------------------------------------|---------------------|------------------------------------------------------------|

| 0003<br>0007        | Clear A Register<br>Clear X Register         | 0315                | Increment X and skip if zero                               |

| 0101                | Test A Register<br>and skip if posi-<br>tive | 0021                | Add A and X,<br>results into A<br>Register, No Skip        |

| 0201                | Test A Register<br>and skip if nega-<br>tive | 0121                | Add A and X,<br>results into A<br>Register—Skip if         |

| 0301                | Test A Register<br>and skip if zero          | 0221                | positive Add A and X, results into A                       |

| 0105                | Test X Register<br>and skip if posi-<br>tive |                     | Register—Skip if negative                                  |

| 0205                | Test X Register<br>and skip if nega-<br>tive | 0321                | Add A and X,<br>results into A<br>Register—Skip if<br>zero |

| 0305                | Test X Register<br>and skip if zero          | 0025                | Add A and X, results into X                                |

| 0011                | Increment A and no skip                      |                     | Register — No<br>skip                                      |

| 0111                | Increment A and skip if positive             | 0125                | Add A and X, results into X                                |

| 0211                | Increment A and skip if negative             |                     | Register—Skip if positive                                  |

| 0311                | Increment A and skip if zero                 | 0225                | Add A and X, results into X                                |

| 0015                | Increment X and no skip                      |                     | Register—Skip if negative                                  |

| 0115                | Increment X and skip if positive             | 0325                | Add A and X, results into X                                |

| 0215                | Increment X and skip if negative             |                     | Register—Skip if zero                                      |

| Instruction<br>Code | Description                                                                    | Instruction<br>Code | Description                                                                                      |

|---------------------|--------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------|

| 0031                | Exclusive OR A with X, Results into A Register—                                | 0355                | Two's complement of X — Skip if zero                                                             |

| 0131                | no skip Exclusive OR A with X, Results into A Register— Skip if positive       | 0061                | Complement A<br>and Exclusive OR<br>with X, Place re-<br>sult in A register<br>— No Skip •       |

| 0231<br>0331        | Exclusive OR A with X, Results into A Register—Skip if negative Exclusive OR A | 0161                | Complement A<br>and Exclusive OR<br>with X, Place re-<br>sult in A register<br>—Skip if positive |

|                     | with X, Results<br>into A Register—<br>Skip if zero                            | 0261                | Complement A<br>and Exclusive OR<br>with X, Place re-                                            |

| 0035                | Exclusive OR A with X, Results into X Register—No Skip                         | 0361                | sult in A register —Skip if negative Complement A                                                |

| 0135                | Exclusive OR A with X, Results into X Register—Skip if positive                |                     | and Exclusive OR with X, Place re- sult in A register — Skip if zero                             |

| 0235                | Exclusive OR A with X, Results into X Register—Skip if negative                | 0065                | Complement X<br>and Exclusive OR<br>with A, Place re-<br>sult in X register<br>— No skip         |

| 0335                | Exclusive OR A with X, Results into X Register—Skip if zero                    | 0165                | Complement X<br>and Exclusive OR<br>with A, Place re-<br>sult in X register                      |

| 0041                | One's complement of A — No skip                                                | 0265                | —Skip if positive<br>Complement X                                                                |

| 0141                | One's complement of A — Skip if positive                                       |                     | and Exclusive OR with A, Place result in X register—Skip if negative                             |

| 0241<br>0341        | One's complement of A — Skip if negative One's complement of A — Skip if zero  | 0365                | Complement X and Exclusive OR with A, Place result in X register — Skip if zero                  |

| 0045                | One's complement of X — No skip                                                | 0071                | Subtract A from<br>X, Place result in<br>A register — No                                         |

| 0145<br>0245        | One's complement of X — Skip if positive  One's complement                     | 0171                | Subtract A from<br>X, Place result in<br>A register — Skip                                       |

| 0345                | of X — Skip if negative  One's complement of X — Skip if zero                  | 0271                | Subtract A from X, Place result in A register—Skip if negative                                   |

| 0051                | Two's complement of A—No skip                                                  | 0371                | Subtract A from X, Place result in A register—Skip                                               |

| 0151                | Two's complement of A — Skip if positive                                       | 0075                | if zero Subtract X from A, Place result in                                                       |

| 0251                | Two's complement of A—Skip if negative                                         | 0.4==               | X Register — No<br>skip                                                                          |

| 0351                | Two's complement of A — Skip if zero                                           | 0175                | Subtract X from<br>A, Place result in<br>X Register—Skip<br>if positive                          |

| 0055<br>0155        | Two's complement of X — No skip Two's complement                               | 0275                | Subtract X from<br>A, Place result in<br>X Register—Skip                                         |

| 0255                | of X—Skip if positive Two's complement of X—Skip if negative                   | 0375                | if negative Subtract X from A, Place result in X Register—Skip if zero                           |

|                     |                                                                                |                     | 7000                                                                                             |

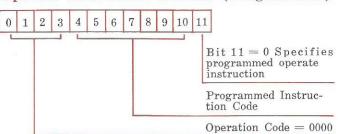

# Operate Instruction Format (Programmed)

| Instruction                                                                                                                                                                                                  |                | Mnemonic | Instruction<br>Code | Cycle |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|---------------------|-------|

| Short Arithmetic R $(A)_{i} \rightarrow A_{i+1} \text{ for } (A)_{\circ} \rightarrow A_{\circ}$                                                                                                              |                | SAR      | 0014                | 1     |

| Short Arithmetic L<br>$(A) \mapsto A_{i-1}$ for $0 \to A_{i-1}$                                                                                                                                              |                | SAL      | 0016                | 1     |

| $\frac{\text{Long Arithmetic Ri}}{(\mathbf{A})_{i} \to \mathbf{A}_{i+1}, (X)}$ $\text{for } 0 \le \mathbf{i} \le 11$ $(\mathbf{A})_{\circ} \to \mathbf{A}_{\circ}$ $(\mathbf{A})_{n} \to \mathbf{X}_{\circ}$ |                | LAR      | 0214                | 1     |

| $\frac{\text{Long Arithmetic Le}}{(A)_{i} \rightarrow A_{i-1}, (X)}$ $0 < i \le 11$ $(X)_{\circ} \rightarrow A_{11}$ $0 \rightarrow X_{11}$                                                                  |                | LAL      | 0216                | 1     |

| $\frac{\text{Short Logical Right}}{(A)_{\text{i}} \rightarrow A_{\text{i+1}}, 0 \leq} \\ 0 \rightarrow A_{\text{o}}$                                                                                         |                | SLR      | 0114                | 1     |

| Short Logical Left $S$<br>$(A) \mapsto A_{i-1}, 0 < 0 \rightarrow A_{i-1}$                                                                                                                                   |                | SLL      | 0116                | 1     |

|                                                                                                                                                                                                              |                | LLR      | 0314                | 1     |

|                                                                                                                                                                                                              |                | LLL      | 0316                | 1     |

| Short Rotate Right $(A)_{:} \to A_{:+1} \text{ for } (A)_{::} \to A_{\circ}$                                                                                                                                 | $0 \le i < 11$ | SRR      | 0010                | 1     |

| Short Rotate Left $(A)_{i} \to A_{i-1} \text{ for } (A)_{\circ} \to A_{n}$                                                                                                                                   | $0 < i \le 11$ | SRL      | 0012                | 1     |

| $\frac{\text{Long Rotate Right}}{(A)_{1} \rightarrow A_{1+1}, (X)_{1}}$ for $0 \le i < 11$ $(X)_{11} \rightarrow A_{0} (A)_{12}$                                                                             |                | LRR      | 0210                | 1     |

| Instruction                                                                                                                                                                                                                                       | Mnemonic    | Instruction<br>Code | n<br>Cycles |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|-------------|

| $\frac{\text{Long Rotate Left}}{(A)_{i} \rightarrow A_{i-1}, (X)_{i} \rightarrow X_{i-1},}$ $0 < i \le 11$ $(X)_{\circ} \rightarrow A_{11}$ $(A)_{\circ} \rightarrow X_{11}$                                                                      | LRL         | 0212                | 1           |

| Short Circulate Right $(A)_{i} \rightarrow A_{i+i}, 0 \le i < 11$ $(A)_{i} \rightarrow CO$ $(CO) \rightarrow A_{\circ}$                                                                                                                           | SCR         | 0110                | 1           |

| $\frac{\text{Short Circulate Left}}{\text{(A)}_{i} \rightarrow \text{A}_{i-1},  0 < i \leq 11}$ $\text{(A)}_{\circ} \rightarrow \text{CO}$ $\text{(CO)} \rightarrow \text{A}_{11}$                                                                | SCL         | 0112                | 1           |

| $\frac{\text{Long Circulate Right}}{(A): \rightarrow A_{1:1}, (X): \rightarrow X_{1:1},}$ $0 \le i < 11$ $(CO) \rightarrow A_{\circ}$ $(A): \rightarrow X_{\circ}$ $(X): \rightarrow CO$                                                          | LCR         | 0310                | 1           |

| $ \begin{array}{c} \underline{\text{Long Circulate Left}} \\ \hline (A): \rightarrow A_{^{i-1}}, \ (X): \rightarrow X_{^{i-1}}, \\ 0 < i \leq 11 \\ (CO) \rightarrow X_{^{11}} \\ (X): \rightarrow A_{^{12}} \\ (A): \rightarrow CO \end{array} $ | LCL         | 0312                | 1           |

| $\frac{\text{Copy Accumulator into Index}}{(A) \to X}$                                                                                                                                                                                            | CAX         | 0240                | 1           |

| $\frac{\text{Copy Index into Accumulator}}{(X) \to A}$                                                                                                                                                                                            | CXA         | 0140                | 1           |

| Exchange Accumulator and Inde<br>$(A) \rightarrow X$<br>$(X) \rightarrow A$                                                                                                                                                                       | ex XAX      | 0040                | 1           |

| Exchange Halves of Accumulate $(A)_{\circ -5} \to A_{\circ -11}$ $(A)_{\circ -11} \to A_{\circ -5}$                                                                                                                                               | or XHA      | 0020                | 1           |

| Halt                                                                                                                                                                                                                                              | HLT         | 0000                | 1           |

| $\frac{\text{No Operation}}{\text{(P)} + 1 \rightarrow P}$                                                                                                                                                                                        | NOP         | 0002                | 1           |

| $\frac{\text{Set Carry On}}{1 \to \text{CO}}$                                                                                                                                                                                                     | SCN         | 0122                | 1           |

| $\frac{\text{Set Carry Off}}{0 \to \text{CO}}$                                                                                                                                                                                                    | SCF         | 0022                | 1           |

| Enable Interrupts Enable Interrupt System                                                                                                                                                                                                         | ENA         | 0322                | 1           |

| Disable Interrupts Disable Interrupt System                                                                                                                                                                                                       | DIS         | 0222                | 1           |

| Clear Interrupt Clear Current Priority Inter                                                                                                                                                                                                      | CLI<br>rupt | 0226                | 1           |

| $\frac{\text{Index State Set}}{1 \to \text{Index State}}$                                                                                                                                                                                         | XSS         | 0234                | 1           |

| $\frac{\text{Index State Reset}}{0 \to \text{Index State}}$                                                                                                                                                                                       | XSR         | 0134                | 1           |

| Instruction                                                                                                                  | ]<br>Mnemonic  | nstructi<br>Code | on<br>Cycles |  |

|------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|--------------|--|

| $\frac{\text{Carry Out Test}}{(P) + 1 \rightarrow P \text{ if CO}} = 1$                                                      | COT            | 0032             | 7            |  |

| $(P) + 2 \rightarrow P \text{ if } CO = 0$<br>Overflow Test<br>$(P) + 1 \rightarrow P, 0 \rightarrow OV; \text{ if } OV = 0$ | OFT<br>= 1     | 0024             | 1            |  |

| (P) $+2 \rightarrow P$ , if OV = 0<br>Memory Protect Error Test<br>(P) $+1 \rightarrow P$ , $0 \rightarrow MPE$ ; if ME      | MPT<br>PE == 1 | 0044             | 1            |  |

| (P) $+2 \rightarrow P$ ; if MPE = 0<br>Input/Output Error Test<br>(P) $+1 \rightarrow P$ , $0 \rightarrow IOE$ ; if IOE      |                | 0046             | 1            |  |

| (P) $+2 \rightarrow P$ ; if IOE = 0<br><u>Load IB From Accumulator</u><br>(A) <sub>2-11</sub> $\rightarrow$ IB               | LDI            | 0036             | 1            |  |

| And Accumulator with Index $(A) \cdot (X) \rightarrow A$                                                                     | AAX            | 0242             | 1            |  |

| $\frac{\text{Load Status Register}}{\text{(A)} \rightarrow \text{Status}}$                                                   | LDS            | 0260             | 1            |  |

| $\frac{\text{Load Accumulator from Switches}}{\text{(Switches)}} \rightarrow A$                                              | LAS            | 0050             | 1            |  |

| $\frac{\text{Store Status Register}}{(\text{Status}) \to A}$                                                                 | STS            | 0060             | 1            |  |

| $\frac{\text{Load IB from Memory}^*}{[(P) + 1]_{0-11} \to \text{IB}}$ $(P) + 2 \to P$                                        | LDM            | 0236             | 1            |  |

| $\frac{\text{Add Carry}}{\text{(A)} + \text{(CO)}} \to \text{A}$                                                             | ADC            | 0054             | 1            |  |

| Carry $\rightarrow$ CO 1 $\rightarrow$ OV, if overflow                                                                       |                |                  |              |  |

| $\frac{OR \ Accumulator \ with \ Index}{(A) + (X) \rightarrow A}$                                                            | AOX            | 0042             | 1            |  |

| Load Double-Length ** $(Q) \rightarrow A, (Q+1) \rightarrow X$                                                               | LDD            | 0276             | 3            |  |

| Store Double-Length** $(A) \rightarrow Q, (X) \rightarrow Q + 1$                                                             | STD            | 0376             | 3            |  |

| Multiply**                                                                                                                   | MPY            | $0074 \\ 0274$   | 9            |  |

| $(A) \times (Q) \rightarrow A, X$<br><u>Divide</u> **                                                                        | DIV            | 0174<br>0374     | 9            |  |

| $(A, X) / (Q) \rightarrow A$ , Remainder                                                                                     | $x \to X$      |                  |              |  |

| Normalize**                                                                                                                  | NOR            | 0072             | 1 + Count    |  |

| $rac{	ext{Store Shift Register}}{0  ightarrow 	ext{A}_{	ilde{0}-5}} \ 	ext{(Shift)}  ightarrow 	ext{A}_{	ilde{0}-11}$       | SSH            | 0066             | 1            |  |

|                                                                                                                              |                |                  |              |  |

|                                                                                                                                        | I        | nstructi | on    |

|----------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------|

| Instruction                                                                                                                            | Mnemonic | Code     | Cycle |

| $rac{	ext{Load Shift Register}}{(	ext{A}_{	ext{o-5}})  ightarrow 	ext{A}_{	ext{o-5}}}{(	ext{A}_{	ext{6-11}})  ightarrow 	ext{Shift}}$ | LSH      | 0266     | 1     |

| Repeat** Repeat following instruction                                                                                                  | RPT      | 0070     | 1     |

| *Available with larger memories<br>**Available with extended arithmetic                                                                | unit     |          |       |

# Input-Output Instruction Format

|   |   |   |   |   |   | _ |   |   | _ |    |    | -                     |

|---|---|---|---|---|---|---|---|---|---|----|----|-----------------------|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |                       |

|   |   | T | _ | L | T |   | L |   | _ |    |    |                       |

|   |   |   |   |   |   |   |   |   |   |    |    | Device Selection      |

|   |   |   |   |   |   |   |   |   |   |    |    | I/0 Command           |

|   |   |   |   |   |   |   |   |   |   |    |    | Operation Code = 0001 |

|   |   |   |   |   |   |   |   |   |   |    |    | Operation Code = 0001 |

|   |   |   |   |   |   |   |   |   |   |    |    |                       |

| I/0 | Commands                                                                                                                               | Mnemonic               | Cycles  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|

| 000 | Transmit to A & Skip                                                                                                                   | TTA                    | 1       |

|     | (Selected device) $\rightarrow$ A, (Selected device) $\rightarrow$ A, (Selected device) is ready (P) + 2 $\rightarrow$ P; if device is |                        | ?;      |

| 001 | Transmit from A & Skip  (A) $\rightarrow$ Selected device, (if device is ready  (P) $+2 \rightarrow P$ ; if device is                  | $P) + 1 \rightarrow I$ | 1<br>P; |

| 010 | Input Device Status                                                                                                                    | DST                    | 1       |

|     | (Device status) $\rightarrow$ A, (P) if device is ready (P) $+ 2 \rightarrow$ P; if device is                                          |                        |         |

| 011 | Skip on device flag $\overline{\text{FLAG} = 0}$ $(P) + 2 \rightarrow P$                                                               | SDF                    | 1       |

|     | $FLAG = 1$ (P) + 1 \rightarrow P                                                                                                       |                        |         |

| 100 | External device executes command in A                                                                                                  | EXU                    | 1       |

| 101 | Terminate Inactivate device                                                                                                            | TMR                    | 1       |

| 110 | Select Device                                                                                                                          | SEL                    | 1       |

| 111 | $\frac{\text{I/O control}}{\text{Select Device}}$                                                                                      | IOC                    | 1       |

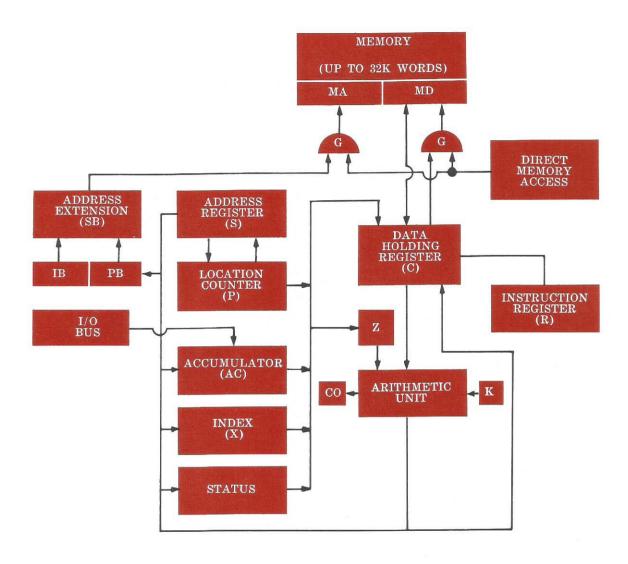

#### INTERNAL MACHINE ORGANIZATION

Figure 1 shows a block diagram of the internal operation of the SCC 650 computer. In this illustration, all arrows indicate data paths and all transfers over these data paths are parallel transfers.

As can be seen from this illustration, the computer contains seven twelve-bit registers, three three-bit registers, three one-bit registers, a parallel adder, and miscellaneous gates and control registers. The operation of these registers is as follows:

DATA PATHS

Figure 1

C Register — The C Register accepts data from the memory and is used as a holding register into the parallel adder. In the halt mode, this register contains the instruction which will be executed next. Execution of the instruction contained in the C Register causes the transfer of the instruction into the R Register which is used to hold the instruction throughout its execution time.

**Z** Register — The Z Register is the second holding register into the parallel adder. The parallel adder uses as its input the output of both the C Register and the Z Register.

X Register — The X Register is a twelve-bit register which can be used for indexing and addressing modification. Microinstructions use the X and the A registers for internal manipulation.

The X Register also serves as the extended accumulator for multiply and divide operations.

A Register—The A Register is the computer's main accumulator. All arithmetic and logical operations performed within the computer use this register to hold the results of the operation.

**R** Register — The R Register holds instructions for decoding into various instruction signals.

P Register— The P Register is a twelve-bit register which is used as the location counter for the computer. When in the relative mode, the six-bit instruction address is added to the contents of the P counter to determine the effective address of the instruction to be executed.

**S** Register — The S Register is the memory address register consisting of twelve bits.

**PB** Register — The PB Register is the instruction extension register used to determine the memory bank from which instructions and all relative operands will be taken.

**IB** Register — The IB Register is the indirect extension register used to specify a particular memory bank for indirectly addressed operands.

**SB Register**— The SB Register is a three-bit register which is decoded and used to specify which memory banks will be used for a particular memory operation.

**Adder** — The twelve-bit parallel adder is capable of arithmetic operations (add and subtract) as well as logical operations such as AND, OR, and EXCLUSIVE OR.

**K** Register — The K Register is a one-bit register used to initiate a carry into the adder. This register is used for two's complement operation and for incrementing registers.

CO Register — The CO Register is a one-bit register which is set when the output of the adder has a carry-out.

**Overflow Register**—The Overflow Register is a one-bit register which is set to "one" when the adder has an overflow.

Status Register—The Status Register is a twelve-bit composite register consisting of:

- (1) The PB register (3 bits)

- (2) The IB register (3 bits)

- (3) The CO register (1 bit)

- (4) The Overflow register (1 bit)

- (5) The Memory Protect register (1 bit)

- (6) The Index State (1 bit)

- (7) The Indirect Indexing State (1 bit)

- (8) The I/O Error register (1 bit)

G Gates— The G Gates serve as a buffer between the central processing unit and memory. When memory is being directly addressed by external devices, the G Gates disconnect memory from the CPU allowing transfer between memory and the external device to take priority. During the time that the external device is using memory, the CPU enters an idle state for one cycle.

Memory — Memory for the computer is broken into eight 4,096 word banks. Memory isolation is provided between the CPU and each bank of memory allowing overlap between memory operations of the CPU and other external devices. If an external device requests a memory bank other than the one being requested by the CPU, both requests are honored simultaneously.

**Switch Register** — A switch register consisting of twelve switches is located on the front panel of the computer. Data can be transferred from the twelve switches into the accumulator under program control. Also, data from these switches may be transferred to any of the active registers during a halt mode operation. In the halt mode, the store switch may be used to store the data contained in the switch register in the memory location specified by the P counter.

# INPUT/OUTPUT FACILITY

Communications with the SCC 650 computer can be accomplished by any of three basic means:

**Programmed Data Transfer**

This facility allows the computer to control the input/output sequence by initiating proper I/O instructions and testing to see if the external device is in a ready state. If the external device is ready, then the computer will initiate a data transfer and skip the next instruction. Programmed data transfer can be initiated by the programmer or by the external device using a program interrupt. Upon receipt of an interrupt from the external device, the computer will trap to the particular subroutine which is programmed to service the interrupting device.

Direct Memory Access

Individual data words or blocks of data can be entered into or taken from the computer memory directly through the direct memory access system. When operating in this mode, the computer will enter an idling state until the external device has completed the data transfer. If the external device is using a memory bank other than the one being requested by the computer, the computer may proceed without intervention. In this case, memory overlap occurs and the external device and the central processing unit are using different banks of memory simultaneously. After initiating a request for memory, the external device does not have to wait until the end of a current instruction to initiate a transfer. The maximum length of waiting time for such a transfer is one computer cycle or two microseconds.

Skip Testing

The computer contains a facility to allow the CPU under program control to request the status of external equipment and, based on the contents of that status, either skip or execute the following instruction. This feature allows the computer to make decisions during the program based on the condition of many external devices.

### OPTIONAL EQUIPMENT

#### **Extended Arithmetic Elements**

This option allows the computer to perform a hardware multiply and divide using the X Register as an extended accumulator. This option also allows for added instructional capabilities for normalizing and scaling of data.

### **Memory Extension Control**

The basic computer can be expanded to include eight banks of memory by using the memory extension control. The control provides all the logic elements necessary for the addition of seven memory banks.

### **Memory Modules**

The basic memory module is a high speed, random access memory with a 1.75 microsecond cycle time consisting of 4.096 twelve bit words.

### High Speed Tape Reader

The high speed paper tape reader is an eight channel photoelectric unit which operates at a rate 300 characters per second

### Paper Tape Punch

Two 8-channel models are available for punching at either 50 or 120 CPS.

#### Card Reader

Punched card readers are available for reading 200 cards or 400 cards per minute.

#### Card Punch

The card punch operates at a punching rate of 100 cards per minute.

#### **Incremental Plotter**

A CalComp Model 565 imcremental plotter and control unit is available for the high speed plotting of points, continuous curves and points connected by lines.

#### Line Printer

This machine prints a selection of 64 characters at the rate of 300 lines per minute and with a 132 character per column format. The vertical format is selected by a punched paper tape within the printer.

### Magnetic Tape Controller

The magnetic tape controller can control up to four magnetic tape decks simultaneously. Each magnetic tape can be controlled to read or write in densities of 200, 556, and 800 bpi and at speeds of from 75 ips to 120 ips.

#### **Magnetic Tape Transports**

The magnetic tape transports will write or read IBM compatible magnetic tape at transfer rates of 15 KC to 96 KC.

#### Magnetic Disc

A magnetic disc unit is available which provides memory in 3 million bit modules with high speed access.

#### Interrupt Clock or Real Time Clock

A clock is available which generates an interrupt within the computer after a preset period of time has elapsed interrupt. Another clock is available for real time input.

## Teletype Input/Output Device

The Model 33 ASR Teletype set can be supplied with each computer. The ASR 33 contains both paper tape reader and paper tape punch in addition to the normal typewriter keyboard. (Optional — ASR 35 Teletype.)

## Pulse Height Adapter

A module is available which in conjunction with an A/D converter will automatically count pulse heights into memory locations.

## Remote Teletype Unit

This option allows the Teletype I/O writer to be remotely located from the central processing unit. (Either 5 or 8 level codes available.)

## Selectric Typewriter

An IBM Selectric Typewriter with a maximum speed of 15.5 characters per second is available. The typewriter is equipped with a pin-feed platen allowing the use of continuous form paper.

## CRT Display

The CRT Display presents X-Y plots of recorded and processed signals for evaluation by the system operator. The system includes two digital to analog converters.

### Analog Multiplexer

This option allows for the sequential sampling of 32 analog channels of 0 to 5 volts DC. The multiplexer contains a buffer amplifier and all the interface necessary for operation with the A-D Converter. The number of channels can vary in groups of two up to the maximum of 32. The computer can address the multiplexer on a random access basis or program the multiplexer for sampling the analog channels sequentially.

## Analog to Digital Converter

The Analog to Digital Converter digitizes the output of the analog multiplexer to an eleven bit plus sign digital data word. Digitizing rates up to 50 KC can be provided. A sample and hold amplifier is included with the analog to digital converter.

## Digital to Analog Converter

The SCC digital to analog converter is an addressable multichannel, binary, two's complement converter. Unit may be bipolar or unipolar with resolutions from 9 to 12 bits.

### MECHANICAL SPECIFICATIONS

#### Standard Cabinet Model

The cabinet model is rack mounted in a standard RETMA 19 inch relay rack, 6 feet in height. The teletype unit is contained on its own stand with the cabinet model. Total weight of the cabinet is 500 pounds. Weight of the Teletype with stand is 40 pounds.

## **Power Requirements**

115 volts, 60 cycle, single phase, at 30 amps. 220 volts can be accommodated on special order.

#### Digital Signal Levels

0 Volts — False, + 8 Volts — True. (Internal) 0 Volts — True + 8 Volts — False. (Interface)

#### SOFTWARE

The SCC 650 includes a symbolic assembler, FORTRAN compiler, utility and math subroutines, and diagnostic routines. Other software is available from a library of programs. Custom programming is available through qualified personnel who are capable of obtaining maximum use and flexibility from the SCC 650.

SCC maintains complete support activities for its users. Installation and maintenance services are available through SCC offices strategically located throughout the United States. For pre-procurement demonstration of hardware and programs in Dallas, contact local sales office or the Marketing Department in Dallas.

#### BARNHILL ASSOCIATES

1170 So. Sheridan Blvd. Denver, Colorado 80226 Phone: 303 934-5505

6101 Anderson St., S.E. Albuquerque, N.M. 87108 Phone: 505 265-7766

3810 Westheimer, Suite 108 Houston, Texas Phone: 713 NA 1-0040

506 N. Central Expressway Richardson, Texas 75080 Phone: 214 AD 1-2573

2721 First Street El Paso, Texas 79925 Phone: 915 598-2442

# COZZENS AND CUDAHY, INC.

9501 W. Devon Avenue Rosemont, Illinois 60018 Phone: 312 825-1144

3712 W. Elm Street Milwaukee, Wis. 53209 Phone: 414 332-0700

7710 Computer Avenue Minneapolis, Minn. 55435 Phone: 612 920-1022

1160 S. Florissant Road Florissant, Missouri 63031 Phone: 314 831-0010

44 Kirk Drive Indianapolis, Indiana 46234 Phone: 317 244-2456-7

# MOXON ELECTRONICS CORPORATION

36 Central Avenue Midland Park, New Jersey Phone: 201 652-6750

40 Coles Avenue Cherry Hill, New Jersey Phone: 609 665-5445

2311 Pontius Avenue Los Angeles, Calif. 90064 Phone: 213 272-9311

15 West 41st Avenue San Mateo, Calif. 94403 Phone: 415 345-7961

#15 No. 40th Place Phoenix, Arizona 85034 Phone: 602 273-7363

# ELECTRONIC SALES ASSOCIATES, INC.

Village Green Crofton, Maryland 21113 Phone: 301 723-0620

#### TECHNICAL ASSOCIATES

2319 East South Street Orlando, Florida 32803 Phone: 305 424-5681

P. O. Box 1443 Huntsville, Alabama 35807 Phone: 205 881-8494

DERMINAL RADIO INTEL, 8 WEST 61st STREET NEW YORK, N. Y. 10023

# **Scientific Control Corporation**

P.O. Box 34529 • 14008 Distribution Way • Dallas, Texas 75234 • 214 — 241-2111

SCC 05-667